Verilog is a powerful and widely-used hardware description language (HDL) that enables engineers to design and simulate digital circuits and systems. Developed in the 1980s, it provides a textual way to represent the structure and behavior of electronic systems, ranging from simple combinational logic to complex microprocessors and systems-on-chip (SoCs).

1. What are the different types of modeling in Verilog?

Ans:

Verilog supports two main types of modeling: behavioral modeling and structural modeling. Behavioral modeling focuses on describing the functionality and operation of a digital system using constructs like procedural blocks and nonstop assignments. Structural modeling, on the other hand, involves defining a system in terms of its factors and their interconnections.

2. What’s Verilog?

Ans:

- Verilog is a hardware description language (HDL) used to model electronic systems.

- It allows designers to describe the structure and behavior of electronic circuits, from simple logic gates to complex digital systems, at various levels of abstraction.

- Verilog can be used for designing and simulating digital circuits, facilitating the design of integrated circuits (ICs) and field-programmable gate arrays (FPGAs).

3. Explain the difference between blocking and non-blocking assignments in Verilog.

Ans:

Blocking assignments in Verilog are carried out sequentially, which means that each statement must finish before the next can start. If this is not handled appropriately, delays may result. Non-blocking assignments, on the other hand, enable the simultaneous execution of numerous statements within a single time step, allowing for more effective modeling and design of intricate behaviors without having to wait for each assignment to complete.

4. What’s the difference between and drivers in Verilog?

Ans:

| Aspect | Drivers | Receivers |

|---|---|---|

| Function | Drivers provide values to signals | Receivers consume values from signals |

| Assignment | Typically assigned using continuous assignments (`assign`) or procedural blocks (`always`) | Values are read within procedural blocks or used in expressions |

| Role in Simulation | Drive the signal values during simulation | React to signal changes and use the driven values |

| Examples | `assign a = b & c;` `always @(posedge clk) a <= b + c;` | `always @(a) b = a + 1;` `if (a == 1) …` |

5. Explain the conception of event- driven simulation in Verilog.

Ans:

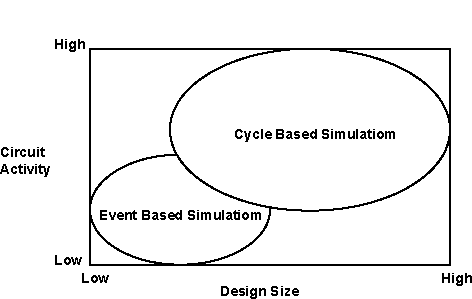

Event- driven simulation in Verilog involves modeling the geste of digital systems grounded on the circumstance of events, similar to changes in signal values. When an event occurs, the affected corridors of the design are estimated, and the simulation progresses consequently. This approach allows for effective simulation by only assessing corridors of the design that are affected by events.

6. What’s a Verilog module?

Ans:

- A Verilog module is an abecedarian structure block used to describe the functionality of a digital circuit or a sub-component within a more extensive system.

- It encapsulates the geste and structure of the tackling element, defining inputs, labor, and internal sense.

- Modules grease hierarchical design and modularization, enabling the exercise of law and simplifying system-position design.

7. How does Verilog handle concurrency?

Ans:

Verilog supports concurrency through the use of procedural blocks, similar to always blocks and original blocks. Within these blocks, multiple statements can execute coincidently, allowing for community in simulation. Verilog also provides constructs like chopstick/ join to explicitly control concurrent prosecution and hierarchical references to manage relations between different situations of the design scale.

8. What are the advantages of using Verilog for tackle design?

Ans:

Verilog offers several advantages for tackle design, including its conciseness, similarity to programming languages like C, and wide assiduity relinquishment. It provides constructs for both behavioral and structural modeling, enabling contrivers to describe complex digital systems in various situations of abstraction. Verilog’s comity with simulation and conflation tools makes it an adaptable choice for FPGA and ASIC design.

9. Explain the difference between a line and a regulation in Verilog.

Ans:

- In Verilog, a line represents a nonstop signal, generally used to connect different modules or factors.

- It’s read-only and can not hold a value assigned within a procedural block. On the other hand, a regulation represents a register or a variable that can have a value assigned within a procedural block.

- While a line is used for interconnections and net affirmations, regulation is used for storing state or temporary values within a module.

10. What’s a testbench in Verilog?

Ans:

A simulation environment designed to verify that a design under test (DUT) is operating as planned is called a testbench in Verilog. It provides a range of input stimuli to the DUT and monitors the outputs to ensure they match the expected results. Before designs are deployed, test benches are crucial for validating and debugging them. They can be developed in Verilog, SystemVerilog, or other languages, giving flexibility in testing techniques and settings.

11. Describe the difference between Verilog and VHDL.

Ans:

Verilog and VHDL are both tackle description languages used for modeling digital systems. While Verilog is more terse and resembles the C programming language, VHDL is more circumlocutory and follows a more strict syntax, suggesting Ada. Verilog is extensively used in assiduity, particularly in the United States, while VHDL is popular in Europe.

12. What’s the significance of conflation in Verilog?

Ans:

- Conflation in Verilog refers to the process of rephrasing a high-position tackle description into a gate-position netlist that can be enforced in silicon.

- It involves converting behavioral or RTL descriptions into a collection of sense gates, flip-duds, and other primitive factors.

- Conflation is a pivotal step in the design inflow, enabling the creation of factual tackle from Verilog law.

13. What are the differences between procedural and non-stop assignments in Verilog?

Ans:

Procedural assignments in Verilog, similar to those within always blocks, are executed successively and are used to model geste that change over time, like state transitions or computations. Nonstop assignments, on the other hand, are used to model combinational sense and are estimated continuously whenever any of their inputs change. Nonstop assignments are generally used for connecting signals within a module and describing concurrent geste.

14. What’s the purpose of parameterized modules in Verilog?

Ans:

- Parameterized modules allow for the creation of applicable and flexible Verilog laws by enabling the specification of customizable parameters when expressing the module.

- Parameters can control various aspects of the module’s geste, such as data range, number of input labors, or configurable functionality.

- Parameterized modules promote law exercise, simplify design variations, and ameliorate scalability by reducing the need for homemade adaptations.

15. Explain the difference between blocking and non-blocking procedural assignments in Verilog.

Ans:

Blocking assignments in procedural blocks( always@( *)) execute successionally, with each assignment waiting for the former one to complete before pacing. They’re used to model combinational senses or coetaneous geste. Non-blocking assignments, on the other hand, are executed coincidentally within the same time step, allowing multiple assignments to be completed contemporaneously.

16. What’s the significance of perceptivity lists in Verilog?

Ans:

Perceptivity lists, specified in always blocks in Verilog, determine when the block is touched off or actuated for prosecution. The perceptivity list indicates which signals or events cause the block to execute when they change. By specifying the applicable perceptivity list, contrivers can directly model the circuit’s geste and ensure effective simulation. It’s crucial to select the sensitivity list carefully to ensure accurate functionality and avoid simulation.

17. How does Verilog handle simulation time?

Ans:

- Verilog uses simulation time to track the progress of the simulation and the ordering of events.

- Simulation time advances separately, and events do at specific simulation time points.

- Verilog provides constructs like delay to schedule events at particular times and posed engage to spark events on rising or falling edges of signals.

- Proper operation of simulation time is critical for directly modeling the geste of digital circuits.

18. What’s the purpose of gate-position modeling in Verilog?

Ans:

Gate-position modeling in Verilog involves describing digital circuits using primitive sense gates like AND, OR, and NOT gates. This position of abstraction is near to the physical perpetration of the design and is generally used for tasks similar to timing analysis, power estimation, and netlist generation for conflation. Gate-position modeling allows contrivers to perform detailed analysis and optimization of the design.

19. How does Verilog handle timing detainments in simulations?

Ans:

Verilog incorporates timing detainments through the use of detention modeling constructs, similar to the driver. These detainments can be specified within procedural blocks to represent the propagation detention of signals through combinational senses or to introduce timing constraints. By directly modeling timing detainments, Verilog simulations can reflect real- world geste, including setup and hold times, signal propagation detainments.

20. Explain the difference between always@( *) and always@( posedge clk) in Verilog.

Ans:

- always@( *) is a perceptivity list used to spark the prosecution of a procedural block whenever any of its inputs change.

- It’s generally used for combinatorial sense or asynchronous processes.

- always@( posedge clk) triggers the block prosecution only on the positive edge of the timepiece signal clk, making it suitable for modeling coetaneous geste, similar to flip-duds and registers, in the successional sense.

21. What are the advantages of using parameterized modules in Verilog?

Ans:

Parameterized modules offer several benefits, including better law exercise, increased inflexibility, and enhanced scalability. By parameterizing modules, contrivers can produce general structure blocks that can be fluently customized and reused across different systems or cases within the same design. This approach reduces redundancy, simplifies design variations, and promotes a modular design methodology.

22. How does Verilog handle inked and unsigned data types?

Ans:

Verilog supports both inked and unsigned data types, allowing contrivers to represent both positive and negative figures. Unsigned data types, similar to regulation and line, represent non-negative integers and are generally used for unsigned computation operations. Inked data types, denoted by inked keyword or$ inked system task, allow the representation of both positive and negative figures using two’s complement garbling.

23. What’s the purpose of the original block in Verilog?

Ans:

- The original block in Verilog is used to initialize variables and execute the law on the morning of the simulation.

- It’s generally used for setting registers’ original values, initializing memory contents, or performing setup tasks before the simulation’s launch.

- Unlike blocks, which execute constantly grounded on specified conditions, original blocks execute only formally on the morning of the simulation, making them suitable for initialization tasks.

24. How does Verilog handle hierarchical design?

Ans:

Verilog supports hierarchical design through the use of modules, allowing contrivers to break down complex systems into lower, manageable modules with well-defined interfaces. Modules can be expressed within other modules, enabling hierarchical association and abstraction of the design scale. This approach promotes law exercise, simplifies design conservation, and facilitates collaboration among multiple contrivers working on different modules.

25. What’s the purpose of always_comb and always_ff constructs in Verilog?

Ans:

- The always_comb construct in Verilog is used to specify combinational sense, ensuring that the statements within the block are estimated whenever any of its inputs change without introducing race conditions.

- always_ff construct is used for successional sense, driving the prosecution of the block on a specific timepiece edge (posedge or engage) to model coetaneous geste, similar to flip-duds and registers.

26. How does Verilog handle the resolution of multiple motorists on the same signal?

Ans:

Verilog uses a resolution medium called the’ last motorist triumphs’ rule to handle conflicts when multiple motorists try to assign values to the same signal. According to this rule, the value assigned by the last executed procedural block or nonstop assignment statement prevails, booting any former assignments. While this medium simplifies rendering, contrivers should be conservative to avoid unintended geste by ensuring proper control of signal assignments.

27. Explain the purpose of the induced construct in Verilog and give an illustration of its operation.

Ans:

- The induced construct in Verilog enables the creation of parameterized and applicable law blocks that can be expressed conditionally grounded on collect-time parameters or conditions.

- It facilitates the generation of repetitious structures, such as arrays of modules or hierarchical designs, without homemade externalization of individual cases.

- For illustration, it can be used to produce an array of adder modules with varying extents grounded on a parameter, perfecting law readability and scalability in complex designs.

28. How does Verilog handle the simulation of asynchronous sense, and what are the challenges associated with it?

Ans:

Verilog simulates asynchronous sense by assessing the geste of circuits that don’t calculate on a timepiece signal for operation, similar to asynchronous resets or asynchronous inputs. Still, bluffing asynchronous senses introduces challenges due to the lack of a global timepiece reference, leading to implicit metastability issues and timing violations. To address these challenges, contrivers must precisely model asynchronous factors, duly attend inputs.

29. What are the differences between line and regulation data types in Verilog, and when to use each?

Ans:

In Verilog, a line is used to represent a nonstop signal or net, generally connecting different modules or factors. It’s read-only and can not retain a value assigned within a procedural block. A regulation represents a register or a variable that can hold a value assigned within a procedural block. Regulation is generally used for storing state or temporary values within a module, making it suitable for successional sense rudiments like flip-duds and registers.

30. What are Verilog resemblant case and entire case statements?

Ans:

- In Verilog, the case statement is used for tentative branching.

- The resemblant case statement, cases, allows do n’t-watch conditions(‘x’s and’ z’) and matches any do n’t-watch condition to the same outgrowth.

- On the other hand, the entire case statement, cases, treats’ x’s and’ z’ as do n’t-watch conditions but doesn’t match x’s or’ z’ against each other.

- This means that cases are more permissive in matching conditions compared to cases.

31. Explain the difference between == and === in Verilog.

Ans:

In Verilog, == is used for equivalency comparison, where two operands are compared for equivalency. It checks if the values of the operands are equal without considering their data types. On the other hand, === is used for equivalency comparison as well, but it performs a strict comparison, checking both the values and the data types of the operands. It returns true only if both the values and the data types are identical.

32. What does the line relate to?

Ans:

In Verilog, a line is a data type used to represent a net, which connects factors within a digital design. Cables are used for hitching different modules or corridors of the design and can represent signals that are continuously driven by one or more sources. Cables are generally used for connections between modules or for representing labor from a combinational sense.

33. What’s reg in Verilog?

Ans:

- In Verilog, reg is a data type used to declare variables that can hold values. Reg is generally used to model storehouse rudiments similar to flip-flops or registers.

- Despite its name, regulation isn’t simply used for registers; it can also represent variables in procedural blocks.

- In simulation, regulation variables retain their values from one simulation cycle to the next, analogous to variables in a programming language.

34. What is the difference between a task and a function in Verilog?

Ans:

In Verilog, tasks and functions are both procedural blocks of law that can contain statements and can be called from other corridors of the design. Still, tasks can contain both input and affair variables and can execute coincidentally with other procedural blocks, while functions are tone-contained blocks of law that return a single value and can be used within expressions.

35. What’s the perceptivity list?

Ans:

In Verilog, the perceptivity list is used in blocks to specify the signals or events that spark the prosecution of the block. The perceptivity list defines the dependencies of the block and determines when the block should be executed. For illustration, in an always@( posedge clk), the perceptivity list( posedge clk) specifies that the block should execute whenever there’s a positive edge transition on the CLK signal.

36. Explain $ examiner, $ display and $ strobe.

Ans:

- In Verilog, $ examiner is a system task used to automatically display the values of variables whenever they change during simulation.

- It continuously monitors the specified variables and prints their values to the simulation press upon change.

- $ display is another system task used to display formatted textbook or variable values to the simulation press during simulation.

- It allows for further control over the display format compared to the examiner.

- $ strobe is analogous to display, but it only shows the specified variables formally at the end of each simulation time step.

37. What’s transport detention?

Ans:

Transport detention in Verilog represents the detention through a sense gate or a path in the design. It models the propagation detention of signals through combinational senses without taking into account setup and hold times. Transport detention is frequently used to model ideal sense gates where signal changes propagate incontinently through the circuit.

38. What’s inertial detention?

Ans:

Inertial detention in Verilog represents the detention through a path in the design while considering the minimal palpitation range needed to spark a change in the affair. It models the geste of actual-world sense gates where input signals must remain stable for a minimal duration before an affair shift is observed. Inertial detention helps capture the flash geste of signals in the design.

39. What are the ways of writing FSM law?

Ans:

- There are several ways to write Finite State Machine( FSM) law in Verilog, including using case statements,- if-additional statements, or state register and coming-state sense.

- One common approach is to use a case statement to define the coming state grounded on the current state and input conditions.

- Another approach is to use separate always blocks for the state register and coming-state sense, with combinational sense to determine the coming state grounded on the current state and input conditions.

40. Explain deposit and force command.

Ans:

In Verilog, the deposit command is used to assign a value to a variable or a memory position at a specific simulation time, allowing for the injection of test stimulants or forcing specific geste during simulation. It’s generally used in test benches for debugging or verification purposes. The force command is analogous to deposit but continuously drives a value into a variable or a memory position until it’s released.

41. Explain snap and drive.

Ans:

In Verilog, the snap command is used to suspend the prosecution of a procedural block, effectively breaking its prosecution until it’s defrosted. It’s generally used in testbenches to halt simulation for debugging or verification purposes temporarily. The drive command is used to force a specific value onto a variable or a signal during simulation. Both snap and drive commands are helpful in controlling simulation geste and debugging.

42. What does timescale 1 Ns/ 1 Ps mean?

Ans:

In Verilog, the timescale directive specifies the units of time used in the simulation. In this case,” 1 Ns/ 1 Ps” means that the simulation time is represented in jiffs( Ns) for integer time units and picoseconds( Ps) for fractional time units. So, a detention of 10 units would represent 10 jiffs, and a detention of 5.5 units would represent 5 jiffs and 500 picoseconds.

43. Which is prioritized first, a variable or a signal?

Ans:

- In Verilog, signals are streamlined before variables during simulation.

- Signals represent physical cables or connections in the design and are streamlined in a listed manner grounded on their perceptivity list or events, similar to timepiece edges.

- Variables, on the other hand, are streamlined within procedural blocks and are estimated and executed successionally grounded on the order of prosecution defined by the simulation scheduler.

44. What’s PLI?

Ans:

PLI stands for Programming Language Interface. In Verilog, PLI is a medium that allows users to affiliate Verilog programs with programming languages like C or C. It enables users to extend the functionality of Verilog simulators by writing custom routines or modules in C/ C that can be called from Verilog law. PLI is generally used for tasks similar to debugging, performance analysis, and uniting Verilog with external tackle or software factors.

45. What are Semaphores?

Ans:

Semaphores are synchronization savages used to control access to participating coffers in a multi-threaded or multi-process terrain. In Verilog, semaphores can be enforced using variables or signals to coordinate access to critical sections of law. They help race conditions and insure that only one process or thread can pierce the participated resource at a time, thereby avoiding conflicts and ensuring data integrity.

46. What’s the plant and plant pattern?

Ans:

- In software engineering, the plant pattern is a creational design pattern that provides an interface for creating objects in a superclass but allows sorts to alter the type of objects that will be made.

- The plant pattern promotes loose coupling by enabling the creation of objects without specifying their concrete classes.

- It’s frequently used in scripts where the creation of objects involves complex initialization or where the exact type of objects demanded is determined at runtime.

47. What’s Callback?

Ans:

A message is a medium used in programming languages to pass a function or system as an argument to another function or system, which can also bring the message function at a later time or in response to a specific event. Calls are generally used in event-driven programming paradigms, similar to asynchronous I/ O operations or user interface relations, where the message function is executed when a particular event occurs.

48. What’s DPI called?

Ans:

DPI stands for Direct Programming Interface. In SystemVerilog, DPI is an extension of the PLI( Programming Language Interface) that provides a standardized medium for uniting Verilog/ SystemVerilog law with foreign languages like C/ C. DPI allows for bidirectional communication between Verilog/ SystemVerilog and C/ C law, enabling tasks, functions, and data to be passed between the two languages seamlessly.

49. What are Parameter and Typedef in Verilog?

Ans:

- In Verilog, parameters are emblematic constants used to define values that can be reused throughout the design.

- They enable the parameterization of modules, allowing contrivers to produce general and applicable designs that can be fluently customized.

- Typedef, short for” type description,” will enable users to define custom data types in Verilog.

- It provides an accessible way to produce aliases for being data types or to describe complex data structures, perfecting law readability and maintainability.

50. Explain some uses of Clocking Blocks.

Ans:

Clocking blocks in SystemVerilog are used to model clocking events and control the timing of signals in a design. They give a way to synopsize clocking-related operations, such as defining timepiece edges, specifying timepiece gating, and coinciding signals. Clocking blocks help ameliorate design readability, modularity, and maintainability by separating clocking-related laws from the main sense, making it easier to understand and remedy clocking issues.

51. What’s the need for an Alias in Verilog?

Ans:

In Verilog, an alias provides an alternate name or reference for a signal or variable. Aliases help create shorter or more descriptive names for signals, perfecting law readability and maintainability. They can also be used to simplify signal assignments or produce logical connections between different corridors of the design. Aliases help make Verilog law more suggestive and easier to understand, especially in large and complex designs.

52. What software is used for Verilog?

Ans:

- Several software tools are used for Verilog design, simulation, and conflation.

- Some popular Verilog tools include Xilinx Vivado, Intel Quartus Prime, Synopsys VCS, Cadence Incisive, and Mentor Graphics ModelSim.

- These tools offer features similar to Verilog law editing, simulation, waveform viewing, conflation, and debugging, making them essential for digital design and verification tasks.

53. In Verilog, what do the cases and case statements mean?

Ans:

In Verilog, cases and cases are tentative branching statements used within case statements. Cases treat’ x’s and’ z’ as do n’t-watch conditions and match them to any value, while cases treat’ x’s and’ z’ as do n’t-watch conditions but don’t match them against each other. Both cases and cases are generally used for specifying multi-way tentative branching grounded on the value of an expression.

54. How can a Sine Wave be produced using Verilog Coding?

Ans:

In Verilog, a sine surge can be produced using ways similar to lookup tables, acceptable algorithms, or behavioral modeling. One common approach is to use a lookup table containing precomputed sine values and fit between them to induce the waveform. Alternately, acceptable algorithms similar to the Taylor series expansion or recursive styles like the CORDIC algorithm can be used to cipher sine values stoutly.

55. Difference between Flip-Flop and Latch.

Ans:

- Flip-flops and latches are both successional sense rudiments used to store double data in digital circuits, but they differ in their design and operation.

- A flip-bomb is edge-touched off, meaning it stores data only on the rising or falling edge of a timepiece signal, furnishing a stable affair between timepiece transitions.

- In discrepancy, a latch is position-sensitive, meaning it stores data as long as its enable signal is asserted, and its affair changes whenever the input changes.

56. What is known about the Verilog event scheduler?

Ans:

The Verilog event scheduler is a pivotal element of the Verilog simulation machine responsible for managing the prosecution of events in the simulation. It maintains a list of slated events and their corresponding timestamps, ensuring that events are executed in the correct order according to simulation time. Events can include changes in signal values, task or function calls, or other simulation events.

57. Explain parameter booting in Verilog.

Ans:

Parameter booting in Verilog allows module parameters to be hoofed during externalization, furnishing a way to customize module cases without modifying the module description. Parameters can be hoofed using the#() syntax in module manifestations, allowing contrivers to specify new parameter values that will be used only for that case. Parameter booting is used for creating parameterized designs where modules can be reused.

58. What’s# 0 in Verilog and its operation?

Ans:

In Verilog,# 0 represents zero simulation time detention and is used to specify immediate prosecution or zero-detention simulation. It’s generally used to model zero-detention events similar to nonstop assignments or immediate signal changes.# 0 is frequently used in a combinational sense or in situations where the simulation requires immediate response to an event, bypassing any slated detainments.

59. Explain Regular Delay Control and Intra-Assignment Delay Control.

Ans:

- Regular detention control in Verilog specifies a fixed detention value that applies to the entire procedural block or statement, using constructs like# n or reprise statements.

- It provides a constant detention for all events within the block, ensuring coetaneous prosecution of statements.

- Intra-assignment detention control, on the other hand, allows specifying individual detainments for specific assignments within a statement, using constructs like directly antedating the assignment.

60. Difference between while and do- while circle.

Ans:

- In Verilog, the white circle and do-while circle are both used for iterative prosecution of statements grounded on a condition.

- Still, the main difference lies in when the condition is checked. In a while circle, the condition is checked before executing the circle body, meaning the circle may Norway execute if the condition is false originally.

- In discrepancy, in a do-while circle, the condition is checked after executing the circle body, ensuring that the circle body is executed at least formally before checking the condition for further duplications.

61. What’s an automatic keyword in the task?

Ans:

- In Verilog, the automatic keyword is used to declare original variables within a task or function with automatic storehouse duration.

- Variables declared with the automatic keyword are created when the task or function is called and destroyed when it exits, ensuring that they’re original to the task or function’s compass and don’t retain their values across multiple conjurations.

- The automatic keyword helps ameliorate law readability and modularity by limiting the compass of variables to the environment in which they’re used.

62. Explain the difference between a static and automatic function.

Ans:

In Verilog, a static function retains its value between calls and has a fixed memory position throughout the simulation. It also behaves as a global function in traditional programming languages. Again, an automatic function allocates memory stoutly upon incantation and releases it upon completion, ensuring that each call creates a new case of the function.

63. Difference between $ stop and $ finish.

Ans:

In Verilog, both $ stop and $ finish are system tasks used to terminate simulation, but they differ in their geste. $ stop suddenly halts the simulation and provides interactive advice for the users to renew or terminate it manually. In discrepancy, $ finish gracefully ends the simulation after completing the current time step and allows the simulation to exit reasonably without user intervention.

64. Difference between $ arbitrary and $ random.

Ans:

Both $ arbitrary and $ random are system functions used to induce arbitrary figures in Verilog. Still,$ arbitrary returns an inked arbitrary number within the full range of representable integer values, while$ random returns an unsigned arbitrary number within the range of 32-bit unsigned integers( 0 to 232- 1).$ arbitrary can return negative values, while$ random always returns non-negative values.

65. Design lapping and non-overlapping FSM for sequence sensor 1010.

Ans:

- Lapping FSM In this design, the FSM transitions to the coming state on each input timepiece edge and can describe the lapping circumstances of the sequence within a single input sluice.

- The state transitions do incontinently upon discovery of the sequence.

- Non-overlapping FSM In this design, the FSM transitions to the coming state only after the entire sequence has been detected, ensuring that posterior circumstances of the sequence are detected only after the former circumstance has been completed.

66. Difference between define and include.

Ans:

In Verilog, define is a preprocessor directive used to define macros or constants that are substituted into the law during compendium. It doesn’t produce a separate train addition but instead replaces the circumstances of the defined macro with its value. Include, on the other hand, is used to include the contents of another Verilog train into the current train during the compendium, allowing for modular law association and exercise.

67. What is FIFO, and what are the conditions for underflow and overflow in a FIFO structure?

Ans:

A data structure known as FIFO (First In, First Out) ensures that the first piece inserted is also the first to be withdrawn. When an attempt is made to read from an empty FIFO, which indicates that no data is accessible, underflow occurs. Conversely, overflow happens when data is added beyond a full FIFO’s capacity, which can result in mistakes, errors, or potential data loss.

68. What are each different operations of FIFO?

Ans:

- FIFOs are operations in various disciplines similar to communication interfaces, data buffering, and synchronization between asynchronous processes.

- Some common operations include softening data between systems operating at different speeds, managing asynchronous data transfers, enforcing channel stages in processors, and controlling access to participating coffers in multi-threaded systems.

- FIFOs are protean and extensively used in digital design to manage data flow and grease communication between different factors or processes.

69. What is a timescale, and what does a timescale of 1 ns/1 ps signify in Verilog?

Ans:

In Verilog, the timescale directive specifies the time units used for simulation and defines the relationship between simulation time and real-time. The directive timescale 1 ns/ 1 ps means that the simulation time is represented in jiffs( ns) for integer time units and picoseconds( ps) for fractional time units. So, a detention of 10 units would represent 10 jiffs, and a detention of 5.5 units would represent 5 jiffs and 500 picoseconds.

70. What are the main exercises of VHDL?

Ans:

VHDL( VHSIC tackle Description Language) is generally used in digital design for various purposes, including modeling and simulation of digital systems, the conflation of tackle designs, and verification of complex systems. Its main exercises include designing digital circuits, specifying system armature, modeling complex geste, performing functional verification, and generating tackle executions from high-position descriptions.

71. List Out Some Of Enhancements In Verilog 2001?

Ans:

- User-defined Primitives (UDPs)

- Automatic Nets

- Configurations

- Generate Blocks

- Configurable Delay Models

- Localparam Declarations

- System Tasks and Functions

- Continuous Assignments Inside Blocks

72. What’s the Difference between Param and typedef in System Verilog?

Ans:

Param and typedef are both used to define a constant, but they serve various purposes. Parameters are used to define collect-time constants or parameters that can be hoofed during externalization, enabling the parameterization of modules. Typedef, on the other hand, is used to define new data types or aliases for being data types, perfecting law readability and maintainability.

73. Why aren’t blocks always allowed in the program block?

Ans:

- In SystemVerilog, blocks aren’t allowed directly within the program block.

- The program block is primarily used for hierarchical association and collaboration of testbench factors, while blocks are used for specifying successional or combinational geste within modules or procedural blocks.

- Placing blocks directly within the program block would violate the hierarchical structure and encapsulation principles of SystemVerilog.

74. What are `chopstick-join`, `chopstick-join_none`, and `chopstick-join_any` in SystemVerilog?

Ans:

For concurrent process execution in SystemVerilog, utilize chopstick-join},chopstick-join_none}, and chopstick-join_any}. Processes created withchopstick-joinexecute concurrently and synchronize at the join statement. Processes that usechopstick-join_none} can function independently without synchronization. By synchronizing at the first join statement encountered, `chopstick-join_any} permits the early termination of other processes and prevents.

75. What’s the difference between mailboxes and ranges in System Verilog?

Ans:

- In SystemVerilog, both mailboxes and ranges are used for communication and synchronization between different vestments or processes.

- Still, mailboxes are primarily used for transferring dispatches between processes asynchronously, furnishing communication-passing semantics.

- Ranges, on the other hand, are used for storing and reacquiring data rudiments in a FIFO(First-In- First-Out) manner, supporting both blocking and non-blocking operations.

76. What’s casting in System Verilog?

Ans:

Casting in SystemVerilog is the process of explicitly converting one data type to another. It allows for flexible data manipulation and ensures proper data handling in expressions or assignments. SystemVerilog provides various casting drivers similar to cast,$ inked,$ unsigned, and bitstream to perform transformations between different data types, including integer, real, vector, and user-defined types.

77. Explain the difference between combinational and successional sense in Verilog.

Ans:

Combinational sense refers to sense circuits where the affair is solely dependent on the current input values, without any memory rudiments. In Verilog, the combinational sense is described using always@( *) blocks or assign statements. A succession sense, on the other hand, includes memory rudiments similar to flip-flops or registers, allowing the affair to depend not only on the current input but also on the former state.

78. What’s the purpose of the induced construct in Verilog?

Ans:

The induced construct in Verilog is used to produce and express modules or sense structures stoutly grounded on collect-time parameters or conditions. It allows for the generation of repetitious or parameterized law without explicitly specifying each case, perfecting law readability and maintainability. Induce constructs are generally used for tentative externalization, array externalization, parameterized modules, and hierarchical designs.

79. How can a latch be inferred unintentionally in Verilog, and how can it be avoided?

Ans:

- An unintentional conclusion of a latch in Verilog can happen when a flip-bomb’s

- Affair isn’t assigned in all possible paths within an always block or when a value is assigned conditionally but not else.

- To avoid unintentional latch conclusion, ensure that every possible path through an always block assigns a value to the affair variable.

80. How to apply a FIFO( First- In- First- Out) buffer in Verilog?

Ans:

A FIFO buffer in Verilog can be enforced using a combination of registers or memory rudiments and control sense to manage data inflow. The design generally includes read and write pointers, storehouse rudiments for data, and control signals for managing buffer status. Data is written into the buffer at the write pointer and read from the buffer at the read pointer, following the FIFO principle.

81. Explain the significance of the posedge and negedge keywords in Verilog.

Ans:

In Verilog, posedge and engage keywords are used to specify edges of timepiece signals in always blocks, indicating rising and falling timepiece edges independently. Podge is generally used to spark conduct on the rising edge of a timepiece signal, similar to streamlining registers or landing input data, while engage is used for conduct on the falling edge. They ensure proper synchronization and timing control in successional sense designs.

82. Explain the differences between Verilog- 1995, Verilog- 2001, and SystemVerilog.

Ans:

- Verilog- 1995 is the original interpretation of the Verilog tackle description language, formalized in 1995 by the IEEE.

- Verilog- 2001 introduced several advancements and new features, including user-defined savages, automatic nets, configurations, induce blocks, and more, to facilitate the language’s expressiveness and usability.

- SystemVerilog, a superset of Verilog- 2001, further extends the language with features for design, verification, and conflation, including object-acquainted programming constructs, data types, interfaces, assertions, and better testbench capabilities.

83. What is the concept of metastability in digital circuits, and how can it be alleviated?

Ans:

Metastability is a miracle in digital circuits where a flip- bomb enters an unstable state due to timing violations, causing it to neither settle to sense high nor sense low. This unstable state can lead to changeable geste and incorrect data prisoners. Metastability can be eased by ensuring proper setup and hold times for signals entering flip-duds, using synchronization ways similar to double-registering or using synchronizer circuits with multiple stages.

84. What are DPI tasks and functions in SystemVerilog, and what issues do they solve in Verilog designs?

Ans:

DPI tasks and functions in SystemVerilog give a medium for uniting Verilog/ SystemVerilog law with foreign programming languages like C/ C. DPI tasks, and functions allow for bidirectional communication between Verilog/ SystemVerilog and C/ C law, enabling the exchange of data, function calls, and complex operations. DPI tasks are used for procedural tasks, while DPI functions are used for functional operations.

85. What is assertion-based verification (ABV) in SystemVerilog, and how do assertions validate designs?

Ans:

- Assertion-grounded verification( ABV) in SystemVerilog is a methodology for vindicating digital designs using formal assertions.

- Written in technical assertion language and bedded directly into the design or testbench law.

- During simulation, assertions are estimated continuously, checking for violations of specified parcels.

- ABV helps describe design bugs, corroborate complex actions, and ensure compliance with design specifications.

86. What is the purpose of `disable` in SystemVerilog assertions, and how does it control activation?

Ans:

The turn-off construct in SystemVerilog assertions is used to control the activation of assertions grounded on specific conditions. It allows assertions to be temporarily impaired or enabled stoutly during simulation grounded on the specified condition. This provides inflexibility in managing assertion activation and allows for picky checking of parcels under different scripts or conditions.

87. What’s meant by” glitch” in digital circuits, and how to avoid them in Verilog designs?

Ans:

- A glitch is a transient and unwanted change in the affair of a digital circuit due to flash changes in the input signals.

- Glitches occur when there are timing mismatches or race conditions in the circuit, leading to changeable geste.

- Glitches can be avoided in Verilog designs by ensuring proper synchronization and timing constraints, using proper timepiece sphere crossing ways, and enforcing adequate sense design practices similar to avoiding asynchronous feedback circles and minimizing signal transitions.

88. How would a Finite State Machine (FSM) be applied in Verilog?

Ans:

A Finite State Machine( FSM) in Verilog is generally enforced using a case statement or a series of- if-additional statements to describe the coming state sense grounded on the current state and input conditions. Each state is represented as a unique value or recitation, and the combinational sense determines the future state grounded on the current state and input signals.

89. What are the advantages and disadvantages of using Verilog for FPGA design compared to VHDL?

Ans:

Advantages of using Verilog for FPGA design include its terse syntax, wide assiduity relinquishment, and expansive tool support. Verilog is also known for its simulation effectiveness and ease of use in digital design. Still, disadvantages include implicit issues with readability and maintainability, as well as differences in language semantics compared to VHDL.

90. What is gate-level modeling in Verilog, and when is it preferred over behavioral modeling?

Ans:

- Gate-position modeling in Verilog involves describing a design using primitive sense gates similar to AND, OR, and NOT gates.

- Gate-position modeling is frequently used for low-position design descriptions where the focus is on the physical perpetration of the circuit rather than its geste.

- It’s generally used for conflation and timing analysis purposes, especially when targeting specific tackle technologies such as ASICs or FPGAs.

LMS

LMS